## Exercices d'électronique, logique MOS

### Exercice 1

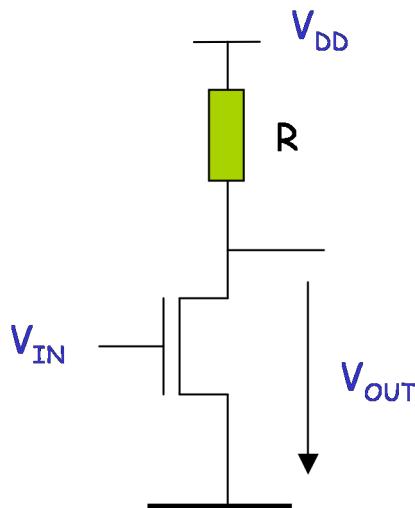

Etude de l'inverseur NMOS ci-contre.

On donne:

$$V_{CC} = 5V, K = 15 \cdot 10^{-6} A/V^2 \text{ et } V_T = 1V.$$

Déterminer la valeur de la résistance R pour assurer un "0" logique avec une tension de 0.6V en sortie.

### Exercice 2

Réaliser une porte XOR en technologie NMOS et CMOS.

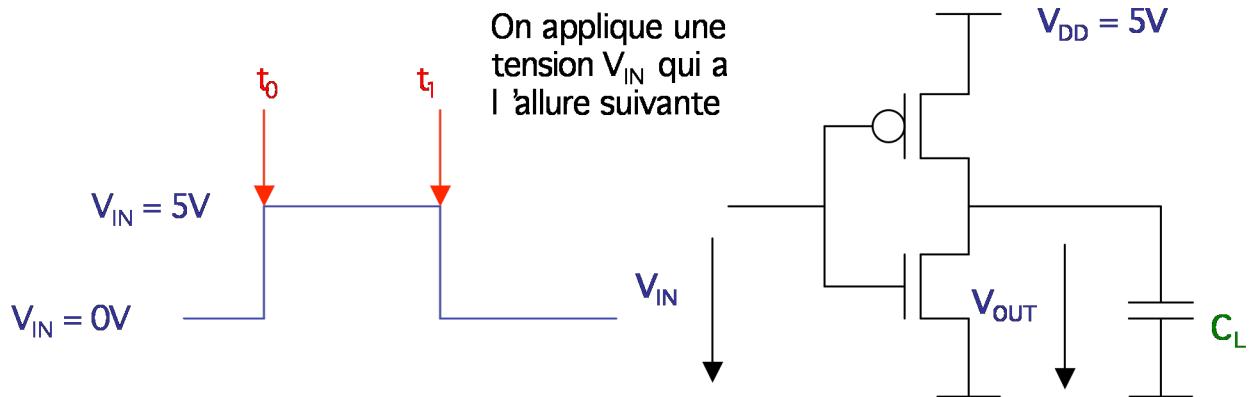

### Exercice 3: Analyse de l'inverseur CMOS

Assimiler  $V_{IN}$  à  $V_{GS}$

On donne:  $V_{TP} = -1 V$  et  $V_{TN} = 1V$ ,  $K_P = K_N = 100 \mu A/V^2$  et  $C_L = 10 \text{ femtoF}$

1. On suppose que la capacité est chargée au départ ( $V_{OUT} = 5V$ ). Dans quel état se trouve le transistor N à l'instant  $t = t_0$

2. Calculer la limite ( $V_{DS} = V_{OUT}$ ) entre la saturation et la linéarité lorsque  $V_{IN} = 5V$

3. Lorsque  $V_{IN} = 5V$ , calculer le  $R_{ON}$  du transistor et la valeur de la source de courant quand le transistor est saturé.

4. Expliquer la méthode utilisée pour évaluer le temps de décharge de la capacité.

Dessiner le schéma analysé à chaque étape en remplaçant le transistor par le modèle le plus adapté.

5. Calculer le temps de décharge permettant de passer de  $V_{DD}$  à  $10\% \cdot V_{DD}$ .

6. Est-il nécessaire de calculer le temps de charge à partir de  $t_1$ . Justifier votre réponse.

7. Quelle est la puissance consommée, si nous travaillons à une fréquence de 100 MHz